锂掺杂的性能提升的黑磷晶体管

作者:GTT 发布于:2019年2月22日

2018年3月29日,微电子器件领域国际顶级学术期刊《IEEE Electron Device Letters》刊发了国家脉冲强磁场科学中心吴燕庆教授课题组利用掺杂提高黑磷晶体管性能的研究成果。该论文标题为“Optimized Transport Properties in Lithium Doped Black Phosphorus Transistors”。吴燕庆教授为论文通讯作者,光电学院2016级博士生高婷婷为第一作者,其余作者包括课题组成员李学飞,熊雄,黄明强,和李调阳。

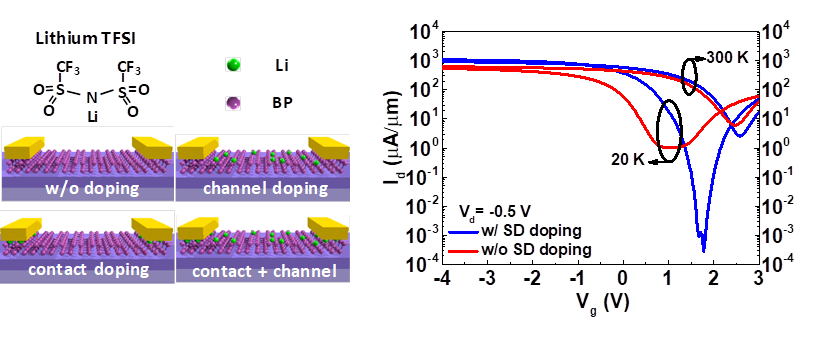

对于传统半导体材料,一般通过掺杂剂扩散或离子注入来进行掺杂,但由于二维的半导体受到维度的限制(在厚度方向上只有一层或少数几层原子),显然传统的掺杂方式不适用于二维原子晶体。因此黑磷与金属的接触是肖特基接触,导致接触电阻很大,严重地制约了器件性能。为了提高黑磷器件性能,需要找到合适的方法减小接触电阻。针对这一问题,我们研究了一种新的锂试剂对器件的源漏进行掺杂的方法,接触电阻从2 kΩ·µm减小到0.85 kΩ·µm,开关比也提高了2.5倍。在20 K时,沟长为0.56微米的黑磷器件的输出电流达到了773 µA/µm.

文章链接:https://ieeexplore.ieee.org/document/8327843