# Tunable 1/f Noise in CVD Bernal-Stacked Bilayer Graphene Transistors

Mengchuan Tian, Qianlan Hu, Chengru Gu, Xiong Xiong, Zhenfeng Zhang, Xuefei Li, and Yanqing Wu\*

Cite This: ACS Appl. Mater. Interfaces 2020, 12, 17686–17690

**ABSTRACT:** Low-frequency noise is a key performance-limiting factor in almost all electronic systems. Thanks to its excellent characteristics such as exceptionally high electron mobility, graphene has high potential for future low-noise electronic applications. Here, we present an experimental analysis of low-frequency noise in dual-gate graphene transistors based on chemical vapor-deposited Bernal-stacked bilayer graphene. The fabricated dual-gate bilayer graphene transistors adopt atomic layer-deposited Al<sub>2</sub>O<sub>3</sub> and HfSiO as top-gate and back-gate dielectric, respectively. Our results reveal an obvious M-shape gate-dependent noise behavior which can be well described by a

quantitative charge-noise model. The minimal area normalized noise spectral density at 10 Hz reaches as low as about  $3 \times 10^{-10} \mu m^2 \cdot Hz^{-1}$  at room temperature, much lower than the best results reported previously for graphene devices. In addition, the observed noise level further decreases by more than 10 times at temperature of 20 K. Meanwhile, the noise spectral density amplitude can be tuned by more than 2 orders of magnitude at 20 K by dual-gate voltages.

**KEYWORDS:** Bernal-stacked bilayer graphene, dual-gate transistors, 1/f noise, charge-noise model, low temperature

# INTRODUCTION

Bernal-stacked bilayer graphene (BLG) is a unique twodimensional semiconductor whose band gap can be tuned by the electric-field-induced broken layer symmetry, making it a promising candidate for electronic applications.<sup>1,2</sup> Significant progress on high-performance Bernal-stacked BLG devices has been made including radio frequency transistors with high voltage and power gain, high-gain active mixers, and low-loss resistive mixers.<sup>3-5</sup> Among these applications, low-frequency noise or 1/f noise plays an important role in the device performance and can become a potential performance-limiting factor. As an example, the 1/f noise can upconvert to higher frequencies by the inherent nonlinearities in field-effect transistors (FETs) and circuits, which can be the main contribution to phase noise of communication systems and sensors.<sup>6,7</sup> To date, the 1/f noise in graphene devices has been studied extensively, and in some cases, the BLG material shows an order of magnitude reduction in noise level compared to that of monolayer graphene (MLG).<sup>8-11</sup> However, most of the above reports are based on the back-gate device structure. Dual-gate device geometry, which is the backbone for practical Bernal-stacked BLG device application, is still largely lacking. Pal and Ghosh<sup>12</sup> reported a V-shape gate bias dependency noise characteristic in dual-gate BLG device where polymethylmethacrylate (PMMA) and mechanically exfoliated BLG were used as top-gate dielectric and channel material, respectively. Heller et al.<sup>10</sup> developed a charge-noise model to

explain M-like shape noise characteristics in mechanically exfoliated MLG and BLG devices where ionic liquid was used as top-gate dielectric. Furthermore, Kumar et al.<sup>13</sup> performed noise measurements in dual-gate hBN-BLG-hBN device, and they found that the gate bias dependent noise characteristic was  $\Lambda$  shape in primary Dirac cone. What we can see is that the gate bias dependence of noise characteristics is very different with different dual-gate dielectrics, indicating the obvious influence of interface characteristics on the noise measurements. On the one hand, dual-gate BLG devices fabricated by mechanically exfoliated BLG are known to suffer from low yield and uncontrollable size, which are serious technological bottlenecks for large-scale applications. On the other hand, growing the gate dielectric by atomic-layer-deposition (ALD) method on top of graphene is highly desired for large-scale applications. The noise characteristics in BLG devices with CVD-grown Bernal-stacked BLG as the channel material and ALD-grown dual-gate dielectrics is limited and has yet to be reported. In this work, we have conducted a thorough study of noise characteristics in dual-gate Bernal-stacked BLG devices

Received: November 19, 2019 Accepted: March 19, 2020 Published: March 19, 2020

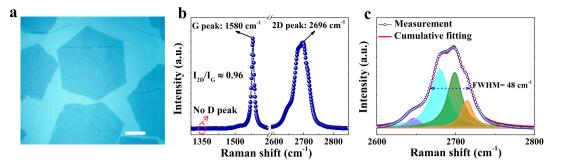

Figure 1. (a) Optical images of the BLG domains transferred onto HfSiO (14 nm)/SiO<sub>2</sub> (90 nm)/Si substrate. Scale bar: 40  $\mu$ m. (b) Raman characterization of the BLG with the excitation laser of 532 nm. (c) 2D peak fitted by four Lorentzian peaks.

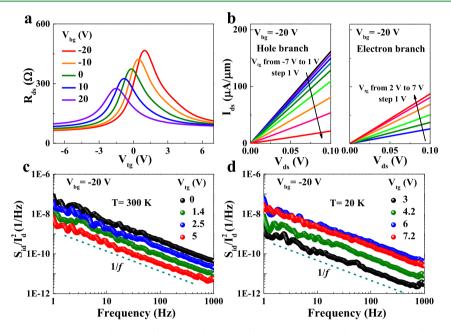

**Figure 2.** (a) Room temperature resistivity as a function of  $V_{tg}$  at different  $V_{bg}$  for the BLG FET with a gate length of 0.3  $\mu$ m. The  $V_{ds}$  is fixed at 0.1 V. (b) Output characteristics of the same device in (a) at  $V_{bg} = -20$  V. (c), (d) Low-frequency noise-normalized spectra  $S_{id}/I_d^2$  as a function of frequency for several  $V_{tg}$  at T = 300 and 20 K, respectively. The  $V_{ds}$  is also fixed at 0.1 V. The ideal 1/f behavior is added for comparison.

with CVD-grown Bernal-stacked BLG as the channel material. Meanwhile, ALD-grown Al<sub>2</sub>O<sub>3</sub> and HfSiO are adopted as topgate and back-gate dielectric, respectively. We find that topgate voltage-dependent 1/f noise exhibits an M-like shape, which is different from most other reported V-shape gate-bias dependence in BLG devices<sup>8,10,12,14</sup> This M-shape gate bias dependency is well explained by a charge-noise model, where the noise can be attributed to charge fluctuation in close proximity to the graphene at low carrier density and scattering in the graphene channel at high carrier density.<sup>10,15</sup> In addition, the minimal area normalized noise spectral density at room temperature reaches as low as about  $3 \times 10^{-10} \ \mu m^2$ . Hz<sup>-1</sup> at 10 Hz, 10 times lower than most of the reported results in the literature.<sup>11,16-18</sup> Furthermore, the noise performance at low temperature has been also demonstrated. The observed noise level decreases more than 10 times and can be tuned by about 200-times of magnitude by changing the dual-gate voltage at temperature of 20 K.

# EXPERIMENTAL AND RESULTS

The Bernal-stacked BLG domains were grown using CVD technique by the thermal decomposition of  $CH_4$  gas in the presence of  $H_2$  gas on a copper foil pocket.<sup>19,20</sup> For a typical growth process, the copper

pocket formed by folding a 25  $\mu$ m thick copper foil was loaded into a 3 in. quartz tube inside a horizontal tube furnace. A gas mixture of 0.5 sccm CH<sub>4</sub> and 60 sccm H<sub>2</sub> flowed across the copper pocket at a temperature of 1070 °C for 2 h, after which the chamber was cooled to room temperature. The detailed BLG growth and transfer procedures are described in our earlier work.<sup>4</sup> In this way, the BLG film transferred onto HfSiO (14 nm)/SiO<sub>2</sub> (90 nm)/Si substrate is shown in the optical microscopy image of Figure 1a. The 90 nm SiO<sub>2</sub> layer is chosen for high visibility of BLG domains under optical microscopy. It has been proven that the high-k HfSiO dielectric with a dielectric constant of 18 contains low surface charge trap density and is expected to improve carrier mobility of graphene channel.<sup>21,22</sup> We can easily distinguish the BLG domains with an approximate hexagonal shape and clear uniform color contrast. The Raman spectrum was used to characterize the number of layers and the stacking order of the graphene. As can be seen in the Raman spectrum of Figure 1b, the peaks centered at 1580 and 2696 cm<sup>-1</sup> correspond to the G and 2D bands, respectively. The intensity ratio between the 2D and G peak is about 0.96. No obvious D peak (centered at 1350 cm<sup>-1</sup>, marked by red dotted part in Figure 1b) is observed in the Raman spectrum, indicating the high quality of the BLG film after being transferred onto the high-k dielectric interface. In Figure 1c, the full width at half-maximum (fwhm) of the 2D peak is 48 cm<sup>-1</sup>. Meanwhile, the 2D peak with an obvious shoulder peak can be wellfitted by four Lorentzian peaks, which is consistent with the characteristics of Bernal-stacked BLG.<sup>23</sup> We further used atomic

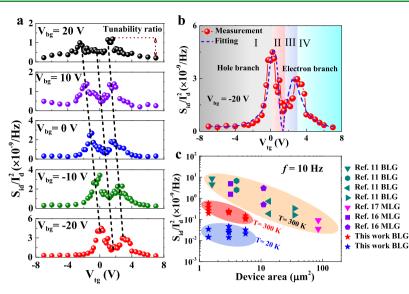

**Figure 3.** (a) Low-frequency noise-normalized spectra  $S_{id}/I_d^2$  at f = 10 Hz versus  $V_{tg}$  at different  $V_{bg}$ . (b)  $S_{id}/I_d^2$  at f = 10 Hz and  $V_{bg} = -20$  V. The blue dot curve represents the result fitted by charge-noise model separately at  $V_{tg} < V_{Dirac}$  and  $V_{tg} > V_{Dirac}$  region. (c) Benchmark for  $S_{id}/I_d^2$  at different device areas.

force microscope (AFM) to confirm the boundary between the BLG domain and MLG film. As shown in Figure S1a,b, the thickness of BLG is about 0.4 nm larger than that of MLG, which is close to the theoretical value of 0.34 nm. The high-quality BLG material provides the basis for the fabrication of BLG devices with low noise level.

After the BLG growth and transfer, BLG FETs with the dual-gate structure were fabricated using nanofabrication process.<sup>4,5</sup> The top gate dielectric consists of a natural-oxidized 2 nm Al seed layer followed by ALD-grown 15 nm Al<sub>2</sub>O<sub>3</sub>. The optical microscopy image and scanning electron microscopy image of the BLG device with twofinger configuration are shown in Figure S1c. Both of the back-gate and top-gate dielectric leakage current are less than 10 pA, as shown in Figure S2a,b. The room temperature resistance of a BLG FET with a gate length of 0.3  $\mu$ m and gate width of 10  $\mu$ m is shown in Figure 2a. The drain-source voltage  $(V_{ds})$  is fixed at 0.1 V, while the top-gate voltage  $(V_{tg})$  is swept from -7 to 7 V with fixed back-gate voltage  $(V_{\rm bg})$  varying from -20 to 20 V. The top-gate charge neutral points (CNPs) change linearly with  $V_{bg}$  related with a slope of about 1/16, as shown in Figure S2c, suggesting larger top-gate coupling strength and the gating efficiency. Similar to those observed in previous studies, tunable peak resistance at CNPs confirms the Bernal-stacked nature of the BLG under displacement electric field.<sup>2,24</sup> While at T = 20 K, the resistivity in CNPs increases and a positive shift in the CNPs is observed, as shown in Figure S4a. The positive threshold voltage shift can be attributed to the frozen trap charges at the oxide/BLG interface at low temperatures.<sup>22,25</sup> Figure 2b shows the output characteristics of the same device in Figure 2a at  $V_{bg} = -20$  V for hole branch (left) and electron branch (right). The output characteristics at T = 20 K is shown in Figure S4b. It can be seen that both output characteristics for the hole and electron branches are highly linear at  $V_{\rm ds}$  ranging from 0 to 0.1 V. Figure 2c,d shows the measured representative normalized noise spectra  $S_{id}/I_d^2$  as a function of frequency at  $V_{\rm bg} = -20$  V for different  $V_{\rm tg}$  at temperatures of 300 and 20 K, respectively. S<sub>id</sub> is the current noise power spectral density and  $I_{\rm d}$  is the drain current through the device channel, and the noise measurement method is similar to that in the literature.<sup>17,26</sup> The noise measurement setup is shown in Figure S3, where the DC biases are provided by Agilent B1500 and the signal source analyzer Agilent E5052B is used to measure the low-frequency noise spectrum together with the Agilent flicker noise system E4725A. It is notable that the noise spectra reveal no obvious traces of the generationrecombination noise. The measured  $S_{id}/I_d^2$  is inversely proportional to the frequency, confirming the 1/f noise nature in the dual-gate Bernal-stacked BLG device.<sup>27</sup> Hooge's empirical relationship with  $S_{id}$

=  $A_{\rm N}I_{\rm d}^2/f'$  is commonly used to characterize the 1/f noise in transistors, where  $A_{\rm N}$  is noise amplitude and  $\gamma$  is a fitting parameter.<sup>17</sup> By fitting the measured data with this empirical relationship, all of the  $\gamma$  values are determined to be close to 1, as shown in Figure S4c,d, indicating that the 1/f noise in the dual-gate BLG device is caused by a collection of fluctuations in channel resistance with a wide distribution of time constant.<sup>27</sup>

To understand the noise mechanism in the dual-gate BLG devices, we studied the correlation of  $S_{id}/I_d^2$  on dual-gate voltage. Figure 3a shows the dependence of  $S_{id}/I_d^2$  on  $V_{tg}$  for different  $V_{bg}$  at f = 10 Hz and T = 300 K. The  $S_{id}/I_d^2$  does not increase monotonically with changing  $V_{te}$ . Instead, the  $S_{id}/I_d^2$  exhibits a notable M-shape gate-bias dependence, where a local valley and two pronounced peaks are clearly visible. Meanwhile, the  $S_{\rm id}/I_{\rm d}^{\ 2}$  shows a weak gate-bias dependence at high  $V_{\rm tg}$  . Notably, the  $V_{\rm tg}$  values for these three special points change with changing  $V_{bg}$ , as shown by black dashed lines in Figure 3a. This variation approximately follows a linear relationship, which is the same as the linear relation between top and back gate voltages in BLG device CNPs, as shown in Figure S5a. This indicates that the charge fluctuations couple to the BLG transistor by effective top-gate and back-gate capacitance and the top-gate capacitive coupling dominates the noise characteristics.<sup>10</sup> This gate dependence of the  $S_{id}/I_d^2$  can be explained by a charge-noise model, where the total noise power spectral density is described by  $S_{id} = S_{input}(dI_{ds}/dV_{tg})^2 + \alpha_s I_{ds}^{4,10,15}$  Among this expression, the  $S_{input}(dI_{ds}/dV_{tg})^2$  term represents the noise associated with random charge fluctuations in the vicinity of channel-oxide interface and the  $\alpha_{s}I_{ds}$ term represents the noise from a gate-independent noise source associated with scattering in the channel. Figure 3b shows a typical comparison of measurement and fitting results at  $V_{bg} = -20$  V. The four different color regions labeled by I to IV in Figure 3b represent that the  $S_{\rm id}/I_{\rm d}^2$  changes monotonically with  $V_{\rm tg}$  at corresponding voltage intervals. The representative  $S_{\rm id}/I_{\rm d}^2$  as a function of frequency at these four different bias regions is illustrated in Figure S6a-d. Given the conductance asymmetry, the hole and electron branches are fitted separately. We observe that the fitting result based on the charge-noise model matches the experimental result very well. As shown in Figure S5b,c, the fitting parameter for  $S_{input}$  at different  $V_{bg}$ are about  $10^{-2}$  mV<sup>2</sup>·Hz<sup>-1</sup>, which is close to previous fitting result under the same BLG device area.<sup>10</sup> When the measurement temperature decreases to 20 K, the charge-noise model also fits the experimental result well, as shown in Figure S5d. It should also be noted that the  $S_{\rm input}$  shows a slight increase but the  $\alpha_{\rm S}$  is 10 times lower than that of room temperature. This finding indicates that the

### **ACS Applied Materials & Interfaces**

noise associated with scattering in the channel is strongly suppressed at low temperature. Moreover, we use the coefficient of tunability ratio (defined on the top right corner of Figure 3a) as a feasible means to assess the capability of noise controlling by dual-gate voltage. The tunability ratio is more than 20 at  $V_{bg} = -20$  V and increases with the increasing device on/off ratio, as shown in Figure S7a,b. The tunability ratio further increases to about 200 at T = 20 K, as shown in Figure S5d. The high tunability of 1/f noise will help design the future graphene-based devices with the best signal-to-noise ratio.<sup>13</sup> Figure 3c shows a benchmark for  $S_{id}/I_d^2$  as a function of device areas with previous work. The noise data for our work is obtained from high  $V_{\rm tg}$ region at different  $V_{\rm bg}$ . As can be seen, the minimal area normalized  $S_{\rm id}/I_{\rm d}^2$  at room temperature reaches as low as about  $3 \times 10^{-10} \ \mu {\rm m}^2$ .  $Hz^{-1}$  at 10 Hz, which outperforms most of the other graphene devices at the same frequency with the same device areas.<sup>11,16–18</sup> Also, the minimum area normalized  $S_{\rm id}/I_{\rm d}^2$  further decreases to 1.5  $\times$  10<sup>-11</sup>  $\mu m^2 \cdot Hz^{-1}$  at a temperature of 20 K. We note that the noise level is not strictly inversely proportional to the device area, which can be attributed to inhomogeneous BLG devices which are fabricated by different BLG domains.<sup>11</sup> The inhomogeneous BLG domains may result in spatial charge inhomogeneity and inhomogeneous trap distribution.<sup>12,14,28</sup> Finally, combined with noise characteristics in other literature,<sup>10,12,13</sup> it can be seen that whether the channel material is MLG or BLG, the gate bias dependency of the noise characteristics mainly rely on the interface characteristics between the graphene channel and gate dielectrics.

On the other hand, we calculate the noise amplitude from the measured normalized noise density using formula

$$A_{\rm N} = \frac{1}{Z} \sum_{j=1}^{Z} f_j \left( \frac{S_{\rm id}}{I_{\rm d}^2} \right)_j$$

where  $\left(\frac{S_{id}}{I_d^2}\right)_j$  is the normalized noise power density measured at the

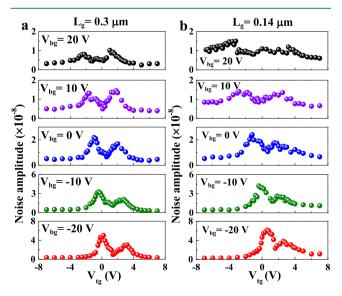

frequency  $f_j$  and  $1 \le f_j \le 1000$  Hz.<sup>16</sup> This definition helps to reduce the measurement errors of the noise at specific frequencies and rule out other types of noise sources. Figure 4a,b shows the room temperature noise amplitude as a function of  $V_{tg}$  at different  $V_{bg}$  for device with  $L_g = 0.3$  and 0.14  $\mu$ m, respectively. It is clearly seen that the dependence of the noise amplitude on  $V_{tg}$  is also a clear M-like shape. Normally, the noise is known to increase with decreasing size.<sup>29</sup> The minimum noise amplitude increases with decreasing device areas, as shown in Figure S8a. The magnitude of noise reflects

**Figure 4.** (a) Noise amplitude as a function of  $V_{tg}$  at different  $V_{bg}$  for device with  $L_g = 0.3 \ \mu$ m. (b) Noise amplitude as a function of  $V_{tg}$  at different  $V_{bg}$  for device with  $L_g = 0.14 \ \mu$ m.

the ability of the conducting channel to screen the external potential fluctuations at the traps. As shown in Figure S8b, the minimum noise amplitude at T = 20 K is as low as about  $3 \times 10^{-10}$ , which is among the best values obtained in graphene devices so far.<sup>8,9,12,13,30</sup>

## CONCLUSIONS

In conclusion, we have studied the noise characteristics in CVD-grown Bernal-stacked BLG. Both of the top and back gate dielectrics in the dual-gate BLG FETs were deposited by the ALD method. The results show that the 1/f noise in the dual-gate BLG FETs exhibits an M-shape gate-bias dependence, which can be well explained by a charge-noise model. Furthermore, the BLG FETs exhibit the lowest noise level compared with previous results and can be reduced even further at low temperatures. Our results provide a coherent description of low-frequency noise in CVD-grown BLG materials, paving the way for its potential applications in the next-generation electronic devices.

# ASSOCIATED CONTENT

#### Supporting Information

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acsami.9b21070.

AFM image for the BLG film and the BLG device structure; detailed characterizations of top-gate and back-gate dielectric layers; noise measurement circuit; dc characteristics at T = 20 K and the fitting parameters of  $\gamma$ at all voltages; peaks positions in the M-shape gate-bias dependence characteristics and the fitting parameters of  $S_{input}$  and  $\alpha_s$  at different  $V_{bg}$ ; representative  $S_{id}/I_d^2$  as a function of frequency at different bias regions; tunability ratio at different  $V_{bg}$  and on/off ratio; and dependence of noise amplitude on device areas and noise amplitude at T = 20 K (PDF)

# AUTHOR INFORMATION

### **Corresponding Author**

Yanqing Wu – Wuhan National High Magnetic Field Center and School of Optical and Electronic Information, Huazhong University of Science and Technology, Wuhan 430074, China; Institute of Microelectronics and Key Laboratory of Microelectronic Devices and Circuits (MOE) and Frontiers Science Center for Nano-optoelectronics, Peking University, Beijing 100871, China; o orcid.org/0000-0003-2578-5214; Email: yqwu@pku.edu.cn

#### Authors

- Mengchuan Tian Wuhan National High Magnetic Field Center and School of Optical and Electronic Information, Huazhong University of Science and Technology, Wuhan 430074, China

- Qianlan Hu Wuhan National High Magnetic Field Center and School of Optical and Electronic Information, Huazhong University of Science and Technology, Wuhan 430074, China

- **Chengru Gu** Wuhan National High Magnetic Field Center and School of Optical and Electronic Information, Huazhong University of Science and Technology, Wuhan 430074, China

- Xiong Xiong Wuhan National High Magnetic Field Center and School of Optical and Electronic Information, Huazhong University of Science and Technology, Wuhan 430074, China

- **Zhenfeng Zhang** Wuhan National High Magnetic Field Center and School of Optical and Electronic Information,

# **ACS Applied Materials & Interfaces**

www.acsami.org

Huazhong University of Science and Technology, Wuhan 430074, China

**Xuefei Li** – Wuhan National High Magnetic Field Center and School of Optical and Electronic Information, Huazhong University of Science and Technology, Wuhan 430074, China

Complete contact information is available at: https://pubs.acs.org/10.1021/acsami.9b21070

## Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

We thank Qiang Liu, Chengcong Cui, Chun Jiang, Yuxi Wang, and Wei Xu in the Center of Micro-Fabrication and Characterization of Wuhan national laboratory for optoelectronics for the support in e-beam lithography and metal deposition. This project was supported by the Natural Science Foundation of China (grant no. 61874162) and the 111 Project (B18001).

## REFERENCES

(1) Oostinga, J. B.; Heersche, H. B.; Liu, X.; Morpurgo, A. F.; Vandersypen, L. M. K. Gate-Induced Insulating State in Bilayer Graphene Devices. *Nat. Mater.* **2008**, *7*, 151–157.

(2) Xia, F.; Farmer, D. B.; Lin, Y.-M.; Avouris, P. Graphene Field-Effect Transistors with High On/Off Current Ratio and Large Transport Band Gap at Room Temperature. *Nano Lett.* **2010**, *10*, 715–718.

(3) Szafranek, B. N.; Fiori, G.; Schall, D.; Neumaier, D.; Kurz, H. Current Saturation and Voltage Gain in Bilayer Graphene Field Effect Transistors. *Nano Lett.* **2012**, *12*, 1324–1328.

(4) Tian, M.; Li, X.; Li, T.; Gao, Q.; Xiong, X.; Hu, Q.; Wang, M.; Wang, X.; Wu, Y. High-Performance CVD Bernal-Stacked Bilayer Graphene Transistors for Amplifying and Mixing Signals at High Frequencies. ACS Appl. Mater. Interfaces **2018**, 10, 20219–20224.

(5) Tian, M.; Li, X.; Gao, Q.; Xiong, X.; Zhang, Z.; Wu, Y. Improvement of Conversion Loss of Resistive Mixers Using Bernal-Stacked Bilayer Graphene. *IEEE Electron Device Lett.* **2019**, 40, 325– 328.

(6) Andreani, P.; Xiaoyan Wang, W.; Vandi, L.; Fard, A. A Study of Phase Noise in Colpitts and LC-Tank CMOS Oscillators. *IEEE J. Solid-State Circuits* **2005**, *40*, 1107–1118.

(7) Moon, J. S.; Curtis, D.; Zehnder, D.; Kim, S.; Gaskill, D. K.; Jernigan, G. G.; Myers-Ward, R. L.; Eddy, C. R.; Campbell, P. M.; Lee, K.-M.; Asbeck, P. Low-Phase-Noise Graphene FETs in Ambipolar RF Applications. *IEEE Electron Device Lett.* **2011**, *32*, 270–272.

(8) Lin, Y.-M.; Avouris, P. Strong Suppression of Electrical Noise in Bilayer Graphene Nanodevices. *Nano Lett.* **2008**, *8*, 2119–2125.

(9) Pal, A. N.; Ghosh, A. Ultralow Noise Field-Effect Transistor from Multilayer Graphene. *Appl. Phys. Lett.* **2009**, *95*, 082105.

(10) Heller, I.; Chatoor, S.; Männik, J.; Zevenbergen, M. A. G.; Oostinga, J. B.; Morpurgo, A. F.; Dekker, C.; Lemay, S. G. Charge Noise in Graphene Transistors. *Nano Lett.* **2010**, *10*, 1563–1567.

(11) Liu, G.; Rumyantsev, S.; Shur, M.; Balandin, A. A. Graphene Thickness-Graded Transistors with Reduced Electronic Noise. *Appl. Phys. Lett.* **2012**, *100*, 033103.

(12) Pal, A. N.; Ghosh, A. Resistance Noise in Electrically Biased Bilayer Graphene. *Phys. Rev. Lett.* **2009**, *102*, 126805-1–126805-4.

(13) Kumar, C.; Kuiri, M.; Jung, J.; Das, T.; Das, A. Tunability of 1/f Noise at Multiple Dirac Cones in hBN Encapsulated Graphene Devices. *Nano Lett.* **2016**, *16*, 1042–1049.

(14) Xu, G.; Torres, C. M.; Zhang, Y.; Liu, F.; Song, E. B.; Wang, M.; Zhou, Y.; Zeng, C.; Wang, K. L. Effect of Spatial Charge Inhomogeneity on 1/f Noise Behavior in Graphene. *Nano Lett.* **2010**, *10*, 3312–3317.

(15) Männik, J.; Heller, I.; Janssens, A. M.; Lemay, S. G.; Dekker, C. Charge Noise in Liquid-Gated Single-Wall Carbon Nanotube Transistors. *Nano Lett.* **2008**, *8*, 685–688.

(16) Stolyarov, M. A.; Liu, G.; Rumyantsev, S. L.; Shur, M.; Balandin, A. A. Suppression of 1/f Noise in Near-Ballistic h-BN-Graphene-h-BN Heterostructure Field-Effect Transistors. *Appl. Phys. Lett.* **2015**, *107*, 023106.

(17) Li, X.; Lu, X.; Li, T.; Yang, W.; Fang, J.; Zhang, G.; Wu, Y. Noise in Graphene Superlattices Grown on Hexagonal Boron Nitride. *ACS Nano* **2015**, *9*, 11382–11388.

(18) Peng, S.; Jin, Z.; Zhang, D.; Shi, J.; Mao, D.; Wang, S.; Yu, G. Carrier-Number-Fluctuation Induced Ultralow 1/f Noise Level in Top-Gated Graphene Field Effect Transistor. ACS Appl. Mater. Interfaces 2017, 9, 6661–6665.

(19) Zhao, Z.; Shan, Z.; Zhang, C.; Li, Q.; Tian, B.; Huang, Z.; Lin, W.; Chen, X.; Ji, H.; Zhang, W.; Cai, W. Study on the Diffusion Mechanism of Graphene Grown on Copper Pockets. *Small* **2015**, *11*, 1418–1422.

(20) Hao, Y.; Wang, L.; Liu, Y.; Chen, H.; Wang, X.; Tan, C.; Nie, S.; Suk, J. W.; Jiang, T.; Liang, T.; Xiao, J.; Ye, W.; Dean, C. R.; Yakobson, B. I.; McCarty, K. F.; Kim, P.; Hone, J.; Colombo, L.; Ruoff, R. S. Oxygen-Activated Growth and Bandgap Tunability of Large Single-Crystal Bilayer Graphene. *Nat. Nanotechnol.* **2016**, *11*, 426–431.

(21) Gao, T.; Li, X.; Xiong, X.; Huang, M.; Li, T.; Wu, Y. Optimized Transport Properties in Lithium Doped Black Phosphorus Transistors. *IEEE Electron Device Lett.* **2018**, *39*, 769–772.

(22) Li, T.; Zhang, Z.; Li, X.; Huang, M.; Li, S.; Li, S.; Wu, Y. High Field Transport of High Performance Black Phosphorus Transistors. *Appl. Phys. Lett.* **201**7, *110*, 163507.

(23) Ferrari, A. C.; Meyer, J. C.; Scardaci, V.; Casiraghi, C.; Lazzeri, M.; Mauri, F.; Piscanec, S.; Jiang, D.; Novoselov, K. S.; Roth, S.; Geim, A. K. Raman Spectrum of Graphene and Graphene Layers. *Phys. Rev. Lett.* **2006**, *97*, 187401-1–187401-4.

(24) Lee, S.; Lee, K.; Zhong, Z. Wafer Scale Homogeneous Bilayer Graphene Films by Chemical Vapor Deposition. *Nano Lett.* **2010**, *10*, 4702–4707.

(25) Zhang, Z.; Xu, X.; Song, J.; Gao, Q.; Li, S.; Hu, Q.; Li, X.; Wu, Y. High-Performance Transistors based on Monolayer CVD MoS2 Grown on Molten Glass. *Appl. Phys. Lett.* **2018**, *113*, 202103.

(26) Li, X.; Li, T.; Zhang, Z.; Xiong, X.; Li, S.; Wu, Y. Tunable Low-Frequency Noise in Dual-Gate MoS2 Transistors. *IEEE Electron Device Lett.* **2018**, 39, 131–134.

(27) Balandin, A. A. Low-Frequency 1/f Noise in Graphene Devices. *Nat. Nanotechnol.* **2013**, *8*, 549–555.

(28) Snow, E. S.; Novak, J. P.; Lay, M. D.; Perkins, F. K. 1/f Noise in Single-Walled Carbon Nanotube Devices. *Appl. Phys. Lett.* **2004**, *85*, 4172–4174.

(29) Hooge, F. N. 1/f Noise is No Surface Effect. *Phys. Lett. A* **1969**, 29, 139–140.

(30) Sun, N.; Tahy, K.; Xing, H.; Jena, D.; Arnold, G.; Ruggiero, S. T. Electrical Noise and Transport Properties of Graphene. J. Low Temp. Phys. 2013, 172, 202–211.